Data-driven lab and field surge tests show compact TVS parts with ∼5.5 V standoff voltages routinely clamp 8/20 μs pulses in the 30–40 A range; understanding their electrical limits and layout requirements is critical to ensure board-level protection without harming signal integrity. This report explains when to pick the PTVS5V5D1BL, how it performs electrically, and exactly how to place and validate it on a PCB, with practical PCB tips and measurable validation checkpoints for design sign-off.

Background — What is the PTVS5V5D1BL and when to use it

Key specs at a glance

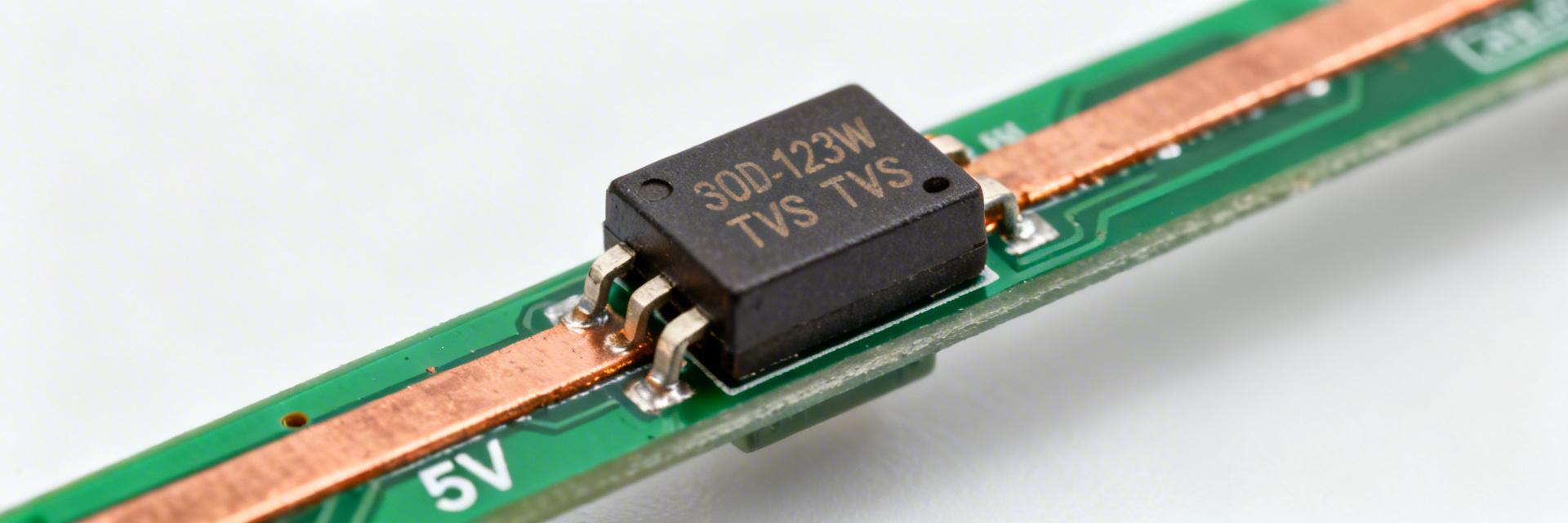

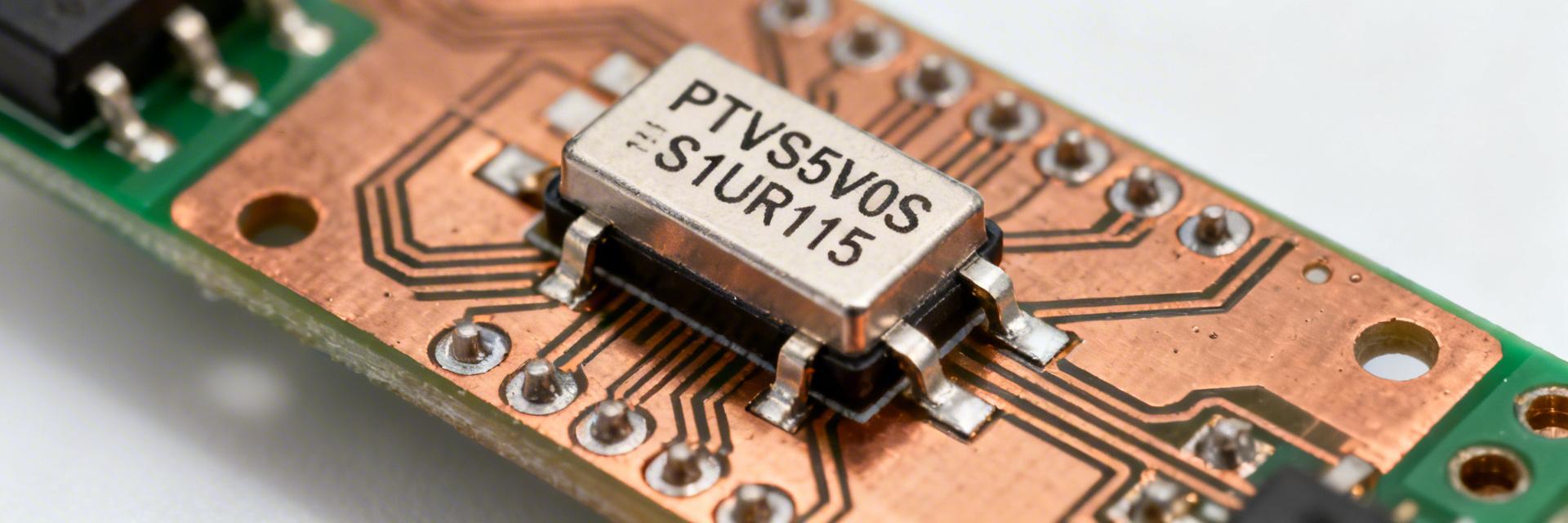

Point: The compact part targets low-voltage rail and I/O protection.

Evidence: Essential specs to scan include VWM (standoff), VBR (breakdown), VCL at 8/20 μs with specified Ipp, peak pulse current rating, diode capacitance, reverse leakage, package (DFN/SMD) and polarity (unidirectional/bidirectional).

Explanation: A one-card spec snapshot (VWM ∼5.5 V, typical clamp at defined Ipp, low pF capacitance) helps decide fit for a given interface quickly.

| Parameter | Symbol | Typical Value | Unit |

|---|---|---|---|

| Standoff Voltage | VWM | 5.5 | V |

| Peak Pulse Current | IPP (8/20 μs) | 30 – 40 | A |

| Diode Capacitance | Cd | Low (pF) | pF |

Typical application threat models

Point: Common threats include ESD (contact/air), EFT bursts, and surge pulses (IEC 61000-4-5 8/20 μs) on power rails or I/O.

Evidence: Designers typically match allowed clamp voltage margin to downstream device absolute maximum ratings.

Explanation: Choose this compact TVS diode when operating rails sit below standoff plus clamp margin, and when surge energy and capacitance trade-offs align with the protected interface requirements.

Datasheet deep-dive — Electrical characteristics & practical performance

Voltage & current behavior (stand-off, breakdown, clamp, Ipp)

Point: Standoff voltage selection and clamp behavior determine whether the TVS prevents damage without unintended conduction.

Evidence: Select VWM slightly above the normal operating voltage so the device stays passive in normal operation; read clamp curves to size protection for expected surge energy using the 8/20 μs Ipp rating. Explanation: For example, if a test pulse delivers 35 A peak and the device clamps at 12 V, estimated pulse energy E≈(Vclamped×Ipp×tpulse)/2 must be compared to PCB trace thermal limits and downstream component avalanche energy ratings to confirm survivability.

Parasitics that matter — capacitance, leakage, dynamic resistance

Point: Parasitic capacitance, leakage, and dynamic resistance influence signal integrity and standby power. Evidence: Capacitance in the single-digit to low-double-digit pF range can degrade high-speed lines; leakage in the microampere range affects low-power bias. Explanation: For high-speed interfaces, limit added capacitance per interface (typical threshold < 5–10 pF); otherwise choose a lower-capacitance TVS class or place the device only on slower lines to balance protection versus performance.

PCB layout & placement guidelines for effective suppression

Placement Rules

Point: Placement proximity is the most impactful layout decision. Evidence: Place the suppression device as close as possible to the connector or IC pin being protected to minimize transient loop inductance. Explanation: Short, wide traces and a low-inductance return reduce overshoot.

Grounding Strategy

Point: Pad geometry and via strategy control thermal spreading. Evidence: Use recommended pad sizes and multiple small thermal vias near ground pads. Explanation: A dedicated ground pad tied to the main plane helps carry surge currents effectively.

Thermal, soldering & reliability considerations

Surge energy dissipation and thermal derating

Point: Repetitive surge exposure and ambient temperature reduce pulse capability. Evidence: Manufacturers specify peak pulse capability at defined test conditions; real-world repetitive duty requires derating. Explanation: Apply conservative derating factors (reduce rated Ipp by a recommended percentage) and increase PCB copper area for heat dissipation.

Assembly and mechanical robustness

Point: Proper reflow and pad metallurgy avoid reliability issues. Evidence: Use footprint recommendations to prevent tombstoning, and follow controlled reflow profiles. Explanation: Post-assembly inspection (X-ray or optical) reduces field failures; consider mechanical support if the board sees significant flexing.

Testing, validation & concise PCB tips checklist

Recommended lab tests and pass/fail criteria

Point: Lab verification must mirror expected field threats. Evidence: Run contact/air ESD per IEC 61000-4-2 and surge tests per IEC 61000-4-5. Explanation: Monitor clamp voltage and downstream node excursions; define pass/fail thresholds tied to downstream absolute maximum ratings.

Quick PCB tips checklist for designers

- ✓ Place the TVS at the board entry point to minimize loop length.

- ✓ Use short, wide traces and stitch ground pad with multiple vias.

- ✓ Verify device capacitance impact on signal bandwidth.

- ✓ Size pads and vias to handle Ipp thermal demands.

- ✓ Run full-system ESD tests under worst-case supply conditions.

Summary

- The PTVS5V5D1BL offers compact SMD surge-clamp capability suitable for low-voltage rail and I/O protection when standoff, clamp voltage, and capacitance match system requirements; prioritize PCB tips and layout to realize device performance.

- Short transient loops, solid returns to plane, and properly sized pads/vias reduce clamp voltage and spread heat during surges; testing under real loads validates assumptions and uncovers integration issues.

- Balance protection and signal integrity: check capacitance vs. interface bandwidth, derate pulse ratings for repetitive events, and include thermal copper or vias when repeated surges are possible.