-

- Contact Us

- Privacy Policy

- term and condition

- Cookies policy

PTVS5V0Z1USKN Datasheet: Key Specs & Electrical Limits

Key Takeaways

- High Surge Capacity: 1,200W peak pulse power protects against severe industrial transients.

- Ultra-Low Clamping: Low Rdyn minimizes voltage overshoot for sensitive 5V logic.

- 80A Peak Current: Industry-leading 8/20 µs robustness for high-exposure ports.

- Compact Footprint: Superior power density compared to standard SMB/SMA packages.

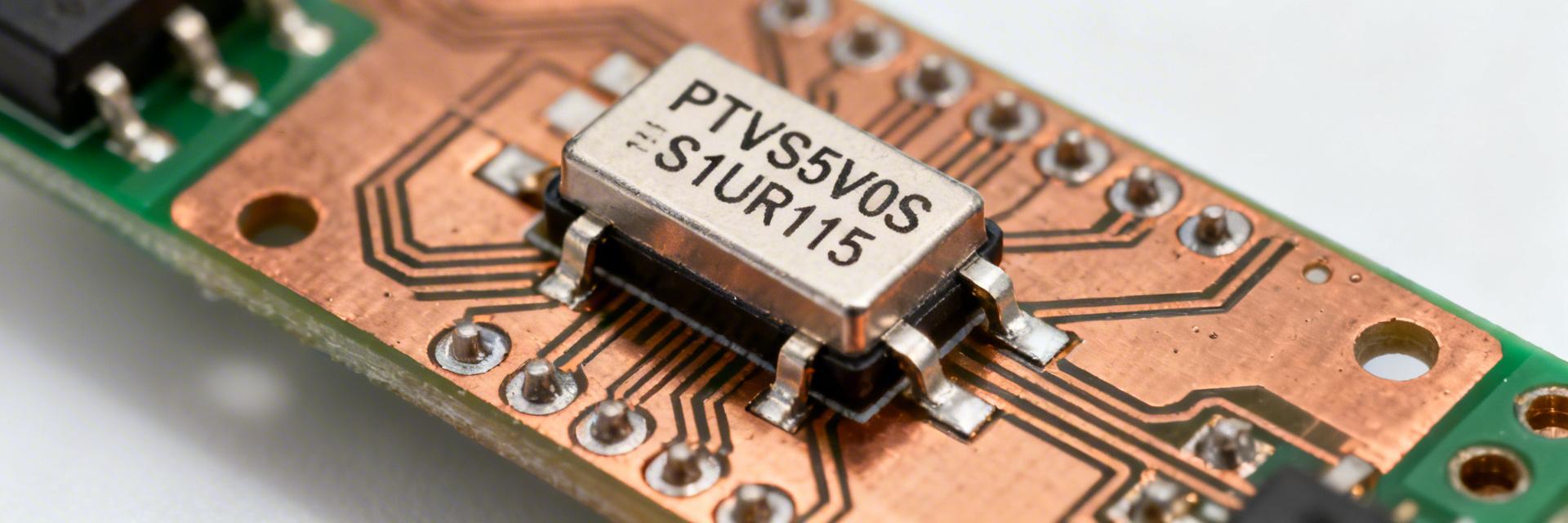

The PTVS5V0Z1USKN transient suppressor delivers industry-relevant peak figures—approximately 80 A (8/20 µs) peak pulse current and up to 1,200 W pulse power—while protecting 5.0 V rails, making those numbers critical when sizing protection for low-voltage digital lines. This article decodes the PTVS5V0Z1USKN datasheet and its electrical specs so designers can translate top-line numbers into design decisions.

Point: designers need a fast, compact reference rather than raw tables. Evidence: the datasheet presents standoff, breakdown, clamping, Rdyn and capacitance in separate sections. Explanation: the goal here is to extract the actionable electrical specs—what limits the part, how it behaves under an 8/20 µs surge, and where layout or derating matters for reliable protection.

Background & quick overview

What the component is and where it's used

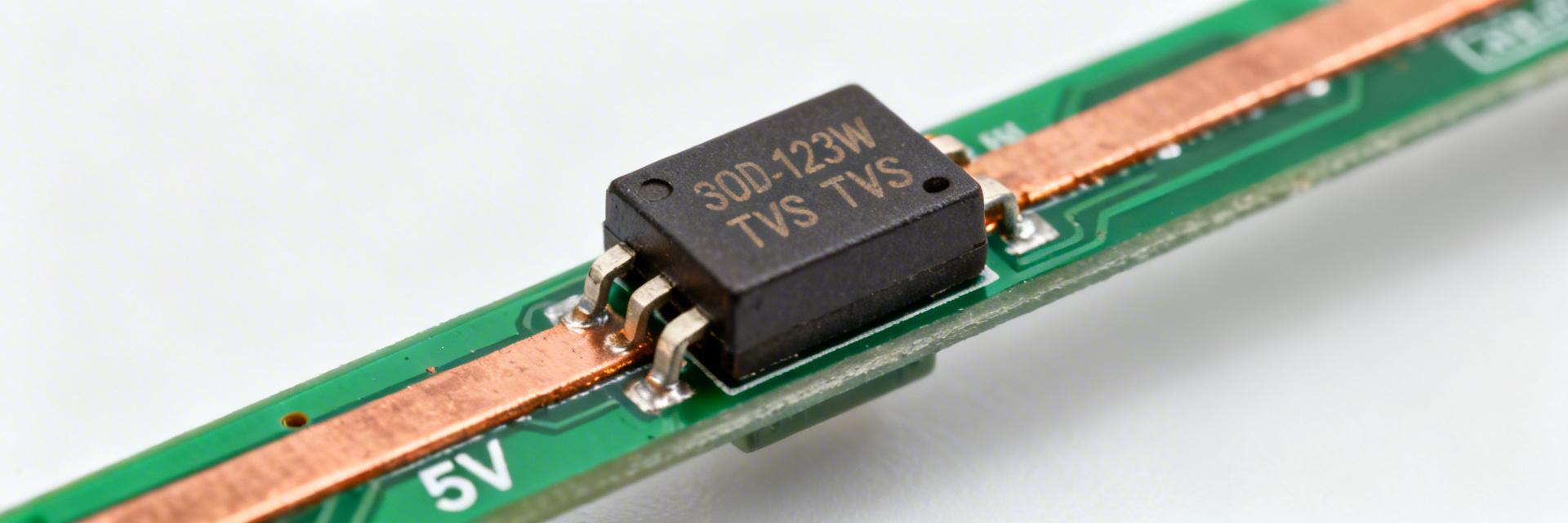

Point: this device is a low-voltage transient voltage suppressor (TVS) intended for 5 V rails and data lines. Evidence: TVS parts are specified to absorb short-duration surges and clamp voltage to protect downstream ICs. Explanation: typical uses include USB power rails, interface lines and low-voltage power domains; for example, a 5 V USB VBUS or an I/O line on a battery-powered module benefits from a compact TVS at the connector.

Quick-spec snapshot (annotated highlights)

Point: designers first scan a compact spec set. Evidence: must-know values are standoff (VWM ≈ 5.0 V), breakdown (VBR range), IPP (~80 A @ 8/20 µs), PPP (~1,200 W @ 8/20 µs), dynamic resistance and capacitance (pF range). Explanation: use this bullet "must-know" set as a quick filter before deeper datasheet reading when comparing parts by rail voltage, surge energy and signal integrity impact.

| Feature / Specification | PTVS5V0Z1USKN | Standard 5V TVS (Generic) | Advantage |

|---|---|---|---|

| Peak Pulse Power (8/20µs) | 1,200 W | 400 - 600 W | 2x Surge Protection |

| Peak Pulse Current (Ipp) | 80 A | 25 - 40 A | Superior Current Handling |

| Dynamic Resistance (Rdyn) | Typ. 0.1 Ω | 0.3 - 0.5 Ω | Better Voltage Clamping |

| Capacitance (Cj) | ~400 pF | 500 - 800 pF | Lower Signal Loading |

Absolute maximums & voltage ratings

Standoff, breakdown and test conditions

Point: standoff (VWM) and breakdown (VBR) define when the diodes begin conduction. Evidence: the datasheet lists VWM near 5.0 V and a specified VBR test current—this is different from clamping voltage measured at IPP. Explanation: designers must check the VBR range and the test current used to define it; breakdown tells when leakage rises and clamping tells how much voltage the protected node will actually see under surge.

Absolute maximum ratings and thermal limits

Point: absolute maxima determine survivability during pulses and repeated stress. Evidence: rated peak pulse power (PPP) and peak pulse current (IPP) are limited by junction temperature and package dissipation. Explanation: exceeding PPP or IPP, or repeated high-energy pulses without derating, can cause junction damage or clamp degradation—designers should follow the datasheet derating curves and limit repeated stress with a safety factor.

Expert Insight: The 5V Rail Trap

"When designing with the PTVS5V0Z1USKN, many engineers overlook the 'clamping margin'. While the standoff is 5V, the clamp voltage at 80A can reach nearly 12V. If your downstream IC has an absolute maximum of 7V or 9V, even this robust TVS won't save it without a series resistor or secondary stage. Always verify the Vc vs. your load's tolerance."

Transient performance & dynamic behavior

Pulse response, clamping voltage and dynamic resistance

Point: clamping voltage at IPP and dynamic resistance (Rdyn) determine the residual voltage seen by protected circuitry. Evidence: clamping is specified for an 8/20 µs waveform and Rdyn is the slope between Vc points. Explanation: for a 5.0 V rail, compute margin by subtracting Vc at expected IPP from rail absolute max; low Rdyn yields less voltage rise for a given current, preserving more margin for sensitive devices.

Capacitance and impact on signal integrity

Point: diode capacitance (single-digit to low-double-digit pF) can disturb high-speed lines. Evidence: datasheet lists typical junction capacitance and notes frequency dependence. Explanation: for USB or fast interfaces, prefer lower-capacitance variants or place the TVS after series resistors/filters; if capacitance is problematic, choose a dedicated low-C data-line TVS or relocate protection to avoid degrading eye diagrams.

How to read the datasheet and compare specs

Typical vs guaranteed values & test conditions

Point: differentiate typical numbers from guaranteed limits. Evidence: datasheets often mark figures as "typical" (measured) or specify limits with test waveform and ambient conditions. Explanation: do not rely on typical clamping voltages for worst-case design; use guaranteed limits and account for temperature and measurement waveform differences when converting bench results into design margins.

Sizing, derating and margin rules of thumb

Point: apply conservative safety factors when selecting a TVS. Evidence: a common rule is to choose IPP ≥ expected surge × 1.25–2 and limit average power for repeated pulses per the datasheet derating curve. Explanation: a simple energy check: required energy (J) ≈ (IPP^2 × Rdyn × pulse duration)/2; compare to part PPP and allow margin for multiple events and PCB thermal limits when laying out the protection strategy.

Application examples & layout recommendations

Hand-drawn schematic, not a precise circuit diagram

Typical application scenarios

Point: different use cases emphasize different specs. Evidence: for 5 V USB power protection, PPP and IPP are primary; for data-line protection, capacitance and clamping voltage matter. Explanation: choose a device with higher energy rating and package for VBUS, and a low-capacitance TVS for D+/D− or high-speed serial lanes to preserve signal integrity while still clamping transients effectively.

PCB placement, footprint and thermal considerations

Point: placement and copper affect surge dissipation and parasitics. Evidence: shortest trace to the protected node, low inductance ground return and sufficient copper pour reduce voltage overshoot and thermal rise. Explanation: place the TVS at the connector with a solid ground return, use wide short traces, and validate with a surge pulse on the bench; thermal imaging under test shows hot spots and helps refine layout or add thermal relief.

Design checklist & troubleshooting

Quick selection checklist (before you place an order)

Point: confirm the critical parameters before procurement. Evidence: check VWM/VBR, IPP and PPP (8/20 µs), capacitance, package fit and operating temperature range. Explanation: reject parts with high capacitance on data lines, insufficient pulse power for expected surge energy, or packages that complicate thermal dissipation; maintain a simple pre-order checklist to avoid late-stage redesigns.

Common failure modes and how to test

Point: overstress and thermal issues are common failures. Evidence: signs include higher clamp voltage, increased leakage or open junction after stress. Explanation: bench tests include controlled 8/20 µs pulses, clamp-voltage measurement at specified IPP and thermal imaging during repeated pulses; establish pass/fail limits and replace parts showing progressive clamp degradation or unacceptable heating.

Summary

- PTVS5V0Z1USKN key electrical specs: standoff ~5.0 V, defined breakdown range, ~80 A IPP (8/20 µs) and ~1,200 W PPP; verify datasheet tables for exact numbers before final design to ensure margins and thermal handling.

- Design actions: use guaranteed clamping voltage and Rdyn when computing margin on a 5 V rail, apply a safety factor to IPP/PPP, and prefer low-capacitance variants for high-speed data lines to preserve signal integrity.

- Layout and validation: place TVS at the connector, keep traces short to ground, thermally verify with pulse tests, and derate for repeated events per the datasheet to avoid clamp degradation.

FAQ

What is the maximum pulse current rating and how does it affect selection?

Point: peak pulse current (IPP) determines the part's ability to absorb a single surge. Evidence: datasheet IPP is specified for an 8/20 µs waveform and should be compared to expected surge scenarios. Explanation: select IPP ≥ expected surge × 1.25–2, check PPP energy limits and ensure PCB thermal capability; if in doubt, choose the next-higher energy-rated package.

How does capacitance affect high-speed data lines?

Point: junction capacitance loads the line and can degrade signal integrity. Evidence: typical capacitance values are in the pF range and vary by part and bias. Explanation: for USB or LVDS, keep TVS capacitance minimal or place the suppressor behind series resistance; validate with eye-diagram testing and choose low-C parts where necessary.

What bench tests validate that the TVS is operating correctly?

Point: controlled pulse and thermal tests reveal reliability. Evidence: apply an 8/20 µs pulse at rated IPP and measure clamping voltage, then perform repeated pulses while observing temperature. Explanation: establish pass/fail thresholds for Vc and thermal rise, use thermal imaging to detect hotspots, and replace parts that show rising clamp voltage or excessive heating after specified numbers of pulses.

- Technical Features of PMIC DC-DC Switching Regulator TPS54202DDCR

- STM32F030K6T6: A High-Performance Core Component for Embedded Systems

- APT50GH120B Datasheet Deep Dive: Specs, Ratings & Curves

- BCM52311A1HH0H275S Datasheet Deep Dive: Key Specs & Metrics

- TL431IDBZR Performance Report: Measured Specs & Limits

- TL431BQDBZR Performance Report: Specs, Thermal Data

- TL431BMFDT datasheet: key specs, tolerances, variants

- TL431BIDBZR: Detailed Specs & Performance Report and Ratings

- TL431AQDBZR Specs Deep Dive: Key Limits & Pinout Explained

- TL431AIDBZR Performance Report: Key Specs & Benchmarks

-

S6008LLittelfuse Inc.SCR 600V 8A TO220

S6008LLittelfuse Inc.SCR 600V 8A TO220 -

CFR-12JB-52-110RYAGEORES 110 OHM 5% 1/6W AXIAL

CFR-12JB-52-110RYAGEORES 110 OHM 5% 1/6W AXIAL -

ECS-F1CE225KPanasonic Electronic ComponentsCAP TANT 2.2UF 20% 16V RADIAL

ECS-F1CE225KPanasonic Electronic ComponentsCAP TANT 2.2UF 20% 16V RADIAL -

ECS-F1HE475KPanasonic Electronic ComponentsCAP TANT 4.7UF 20% 50V RADIAL

ECS-F1HE475KPanasonic Electronic ComponentsCAP TANT 4.7UF 20% 50V RADIAL -

ECS-F1HE335KPanasonic Electronic ComponentsCAP TANT 3.3UF 20% 50V RADIAL

ECS-F1HE335KPanasonic Electronic ComponentsCAP TANT 3.3UF 20% 50V RADIAL -

ECS-F1HE155KPanasonic Electronic ComponentsCAP TANT 1.5UF 20% 50V RADIAL

ECS-F1HE155KPanasonic Electronic ComponentsCAP TANT 1.5UF 20% 50V RADIAL -

CFR-50JB-52-1RYAGEORES 1 OHM 5% 1/2W AXIAL

CFR-50JB-52-1RYAGEORES 1 OHM 5% 1/2W AXIAL -

MM74HC4050NonsemiIC BUFFER NON-INVERT 6V 16-PDIP

MM74HC4050NonsemiIC BUFFER NON-INVERT 6V 16-PDIP -

CFR-50JB-52-1KYAGEORES 1K OHM 5% 1/2W AXIAL

CFR-50JB-52-1KYAGEORES 1K OHM 5% 1/2W AXIAL -

CFR-25JB-52-1KYAGEORES 1K OHM 5% 1/4W AXIAL

CFR-25JB-52-1KYAGEORES 1K OHM 5% 1/4W AXIAL