-

- Contact Us

- Privacy Policy

- term and condition

- Cookies policy

PTVS58VS1UR Datasheet Deep Dive: Key Specs & Ratings

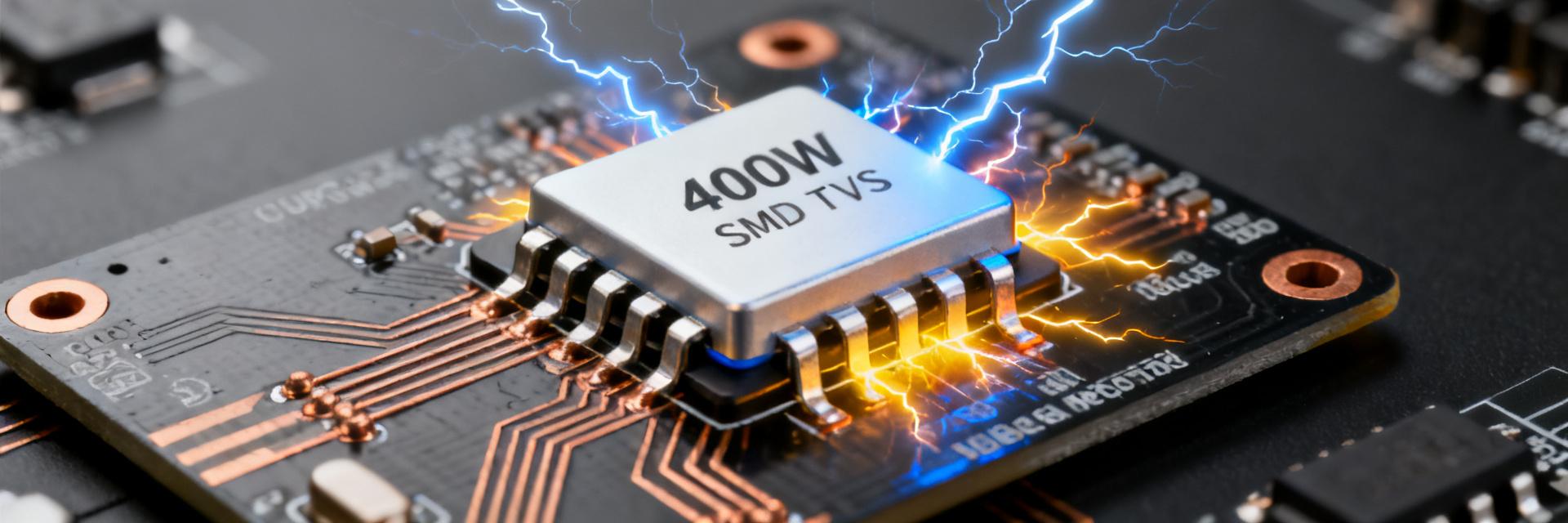

The PTVS58VS1UR is presented in the manufacturer datasheet as a 400 W-class, unidirectional transient voltage suppressor in a low-profile SMD package — a spec set that positions it for board-level surge protection where high-energy transients occur. This introduction summarizes why the datasheet numbers matter, how to extract the critical ratings, and what to verify on samples before committing to production. The goal is a concise, data-driven roadmap that turns tabulated values and curves into actionable selection and layout decisions.

Device background: PTVS58VS1UR — what the top-line specs mean

Package, configuration & top-line ratings

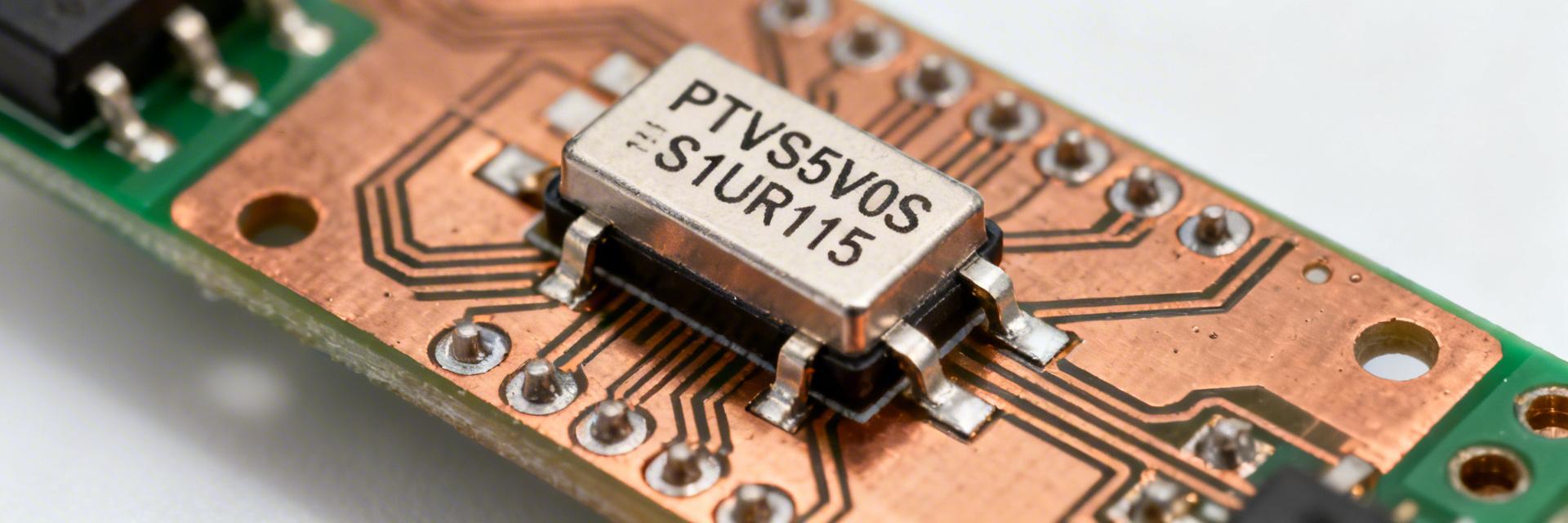

Point: The part is supplied in a low-profile SMD package with a unidirectional configuration, typically a SOD-like footprint with two terminals.

Evidence: The datasheet lists package dimensions and pin count consistent with compact surge clamps.

Explanation: This packaging reduces standoff height and eases placement near protected nodes, while the unidirectional polarity mandates use on DC rails or polarity-sensitive interfaces. Headline ratings to read from the datasheet are peak pulse power (400 W class), standoff voltage (Vwm), breakdown voltage range (VBR), clamping voltage (Vc) at defined Ipp waveform, and leakage current at Vwm. These determine whether the device meets system surge and standby leakage constraints and impact footprint and thermal design.

Typical use cases and system roles

Point: The device is intended for board-level protection on power rails and sensitive interfaces exposed to surge energy.

Evidence: Datasheet application notes typically show use on 12 V–48 V rails and on low-inductance nodes.

Explanation: Choose this 400 W-class unidirectional part for systems that occasionally see high-energy pulses where clamping energy and peak current matter, such as power input lines, motor-drive control boards, and industrial interface protection. For lower-energy environments or where reversible polarity is required, select a lower-power or bidirectional TVS respectively; the trade-offs are clamping performance, size, and standby leakage.

Datasheet deep specs: electrical characteristics & curves

Voltage & current specs to prioritize

Point: Prioritize standoff voltage (Vwm), breakdown voltage (VBR), test current (It), clamping voltage (Vc) and peak pulse current (Ipp) when judging suitability.

Explanation: Read Vwm as the normal operating ceiling — pick a Vwm slightly above nominal bus voltage to limit leakage. VBR tolerance affects how early avalanche begins; Vc under the datasheet’s pulse waveform gives the worst-case clamp the protected node will see.

Transient power, energy handling

Point: The datasheet’s 400 W peak-pulse rating is waveform-dependent and must be interpreted via listed shapes.

Explanation: Peak pulse power alone is not an energy metric — check avalanche energy or pulse-energy vs. duration curves. Use derating graphs to translate real surges into equivalent loads at operating temperatures.

Thermal & reliability considerations

Thermal resistance & junction temperature guidance

Point: RθJA and RθJL and the maximum junction temperature in the datasheet are the basis for thermal calculations.

Explanation: Compute delta-T to estimate junction rise for your worst-case surge. PCB copper area and thermal vias reduce effective RθJA; specify pad sizes and pours per the datasheet recommendations to achieve required derating.

Reliability parameters and screening points

Point: Check junction and storage temperature ranges, soldering profile notes, and mechanical tests.

Explanation: Ensure your soldering profile matches manufacturer recommendations to avoid latent damage, and include thermal cycling in qualification to validate lifecycle expectations.

How to apply in designs: Selection & layout

| Parameter | Why it matters | Action |

|---|---|---|

| Vwm (standoff) | Defines continuous operating limit | Pick Vwm > bus voltage; check leakage |

| VBR | Where avalanche begins | Confirm worst-case VBR within headroom |

| Vc @ Ipp | Maximum transient node voltage | Ensure clamp |

PCB footprint, placement and test setup

Point: Minimize loop inductance and thermal resistance by placing the device close to the protected node with short, wide traces.

Explanation: Place the TVS adjacent to the connector, avoid long traces, and include ground returns with low inductance. For test validation, use a defined surge generator and measure Vc, Ipp, and temperature rise.

📋 Summary

- Confirm the PTVS58VS1UR datasheet’s headline numbers: 400 W pulse class, Vwm as specified by part, VBR range, Vc at Ipp, and leakage — use these as the single source of truth for margins.

- Match Vwm slightly above operating bus, ensure clamp voltage stays below the downstream device limit, and verify leakage at operating temperature to meet system budgets.

- Apply PCB best practices: minimal loop inductance, recommended pad geometry, and sufficient copper for thermal dissipation; validate using defined surge waveforms and thermal checks.

- Run batch verification: leakage, breakdown, clamping, solderability and thermal cycling; confirm part marking and traceability before production buy-in.

FAQ

How should I verify clamping performance during bench testing?

Use a calibrated surge generator with the pulse waveform specified in the datasheet, measure voltage at the protected node with low-inductance probes, record Ipp and resulting Vc, and compare to datasheet Vc. Repeat at expected operating temperature and on representative PCB fixtures to capture real-world parasitics.

What margin is recommended between Vwm and nominal bus voltage?

Choose Vwm approximately 10–20% above nominal for common DC rails to control leakage while preserving headroom; adjust margin based on downstream device sensitivity and measured VBR spread on samples.

Which PCB layout practices most reduce thermal and electrical stress on the TVS?

Place the TVS close to the connector or protected node, use wide short traces, provide a solid copper pour for heat spreading, add thermal vias under the pad if allowed, and minimize loop area between the TVS and return path to reduce inductive overshoot.

- Technical Features of PMIC DC-DC Switching Regulator TPS54202DDCR

- STM32F030K6T6: A High-Performance Core Component for Embedded Systems

- APT50GH120B Datasheet Deep Dive: Specs, Ratings & Curves

- BCM52311A1HH0H275S Datasheet Deep Dive: Key Specs & Metrics

- TL431IDBZR Performance Report: Measured Specs & Limits

- TL431BQDBZR Performance Report: Specs, Thermal Data

- TL431BMFDT datasheet: key specs, tolerances, variants

- TL431BIDBZR: Detailed Specs & Performance Report and Ratings

- TL431AQDBZR Specs Deep Dive: Key Limits & Pinout Explained

- TL431AIDBZR Performance Report: Key Specs & Benchmarks